随着区块链网络不断扩展,节点之间的通信效率逐渐成为性能瓶颈。公共互联网在延迟、拥塞与安全性方面的局限,使得验证器之间的数据传输难以满足高频交易与实时应用的需求,尤其是在 DeFi 与链游等场景中,这一问题更加突出。

在此背景下,DoubleZero 通过 DePIN 模式整合全球私人光纤资源,构建一个独立于公共互联网的高性能通信网络。作为网络基础设施层的重要组成部分,其通过任务调度与验证机制优化数据传输路径,从而在 DePIN 赛道中占据关键位置,并推动 Web3 应用向更大规模发展。

去中心化任务调度与验证机制的重要性

在去中心化网络中,如何高效分配资源并确保执行结果可信,是系统设计的核心问题。任务调度决定了数据如何在不同节点之间流转,而验证机制则确保这些数据在传输和处理过程中不被篡改或伪造。

DoubleZero 通过去中心化调度机制,根据节点性能动态分配任务,避免了中心化系统中的单点故障问题。同时,链上验证机制可以实时审计节点行为,防止作弊或低效运行。这种“调度 + 验证”的组合,是实现低延迟与高可靠性的关键。

DoubleZero 的赛道定位

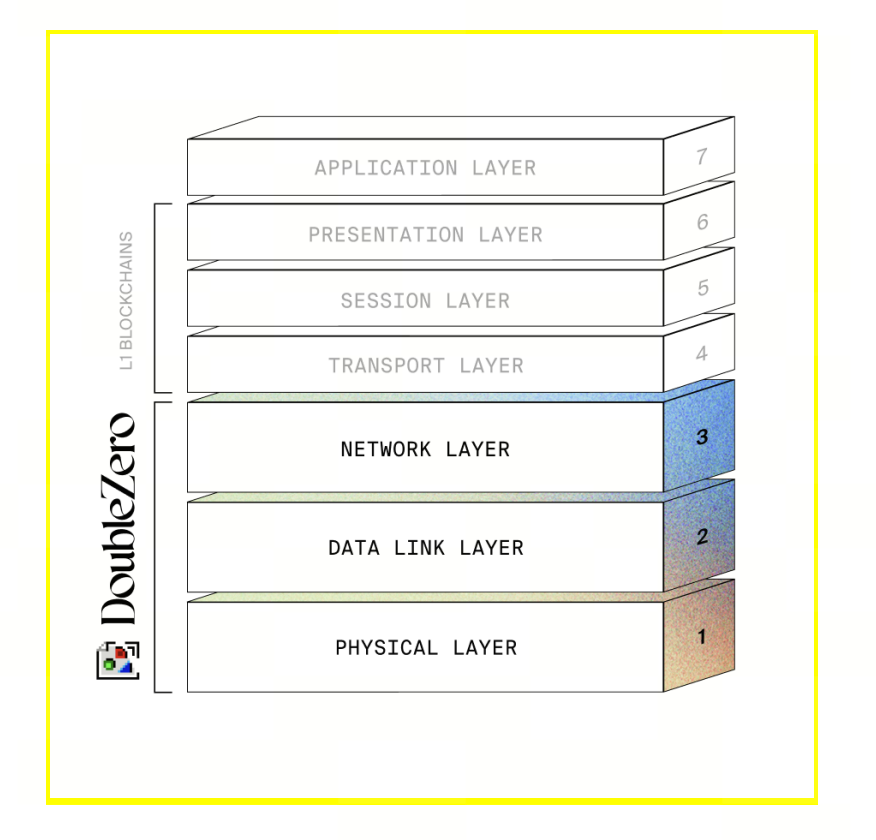

DoubleZero 专注于 DePIN 网络基础设施层,其核心目标是优化数据传输而非计算本身。与 GPU 渲染或算力网络不同,DoubleZero 更关注通信效率,通过边缘过滤与专用带宽提升整体系统性能。

这一定位使其成为区块链网络的“底层加速器”,特别适用于共识优化、实时数据同步以及高频交互场景,在 DePIN 生态中具有独特价值。

DoubleZero 网络的核心参与者有哪些?

DoubleZero 网络由多个角色共同构成,这些参与者在网络中承担不同职责,并通过代币机制形成协作关系。

带宽贡献者通过部署专用设备并提供光纤链路,为网络提供基础传输能力。计算资源贡献者则运行相关软件,处理网络监控与数据反馈。验证者节点通过接入网络提升区块链共识效率,而开发者则通过 API 接入网络服务,将其应用于具体场景。

这些角色共同构成了一个分布式协作体系,使网络能够持续扩展并保持高性能运行。

DoubleZero 的任务调度机制详解

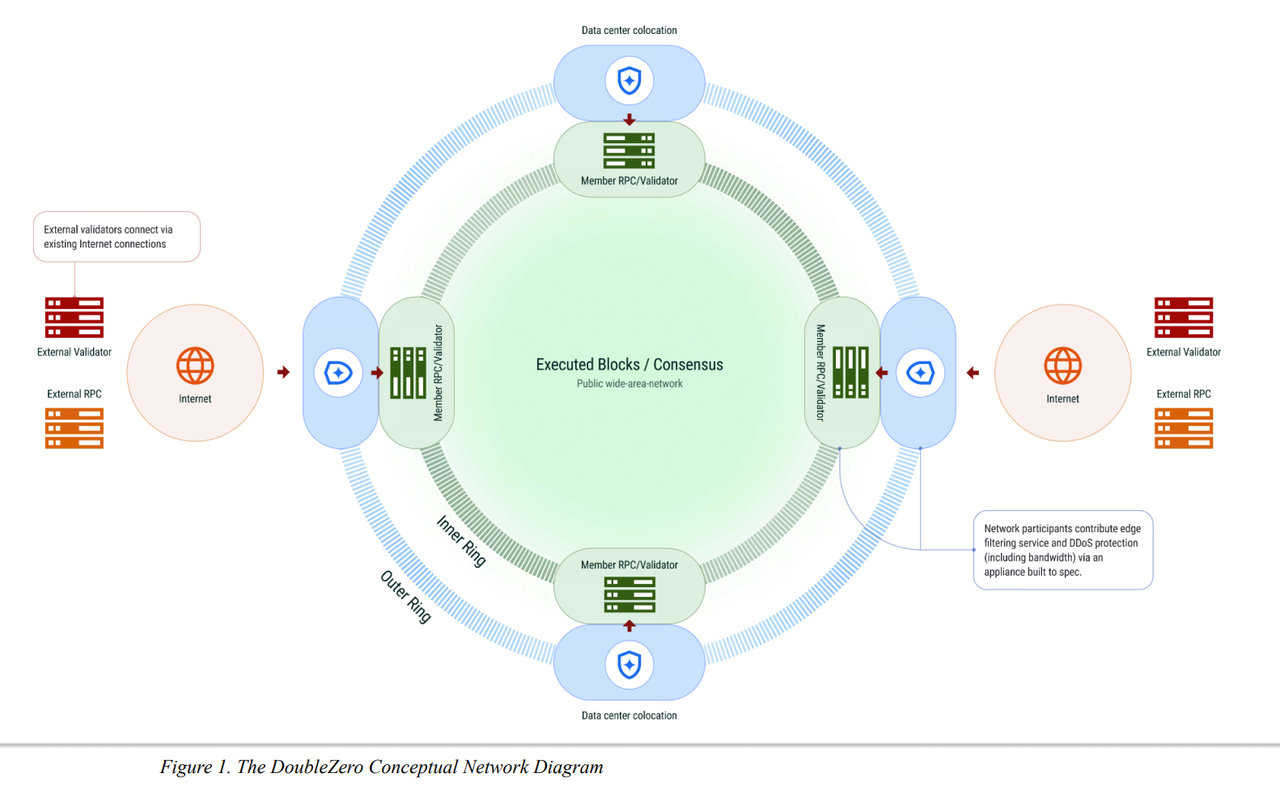

DoubleZero 的任务调度由链上智能合约驱动,并结合多层软件组件实现动态分配。系统首先通过控制器将链上数据转化为路由规则,然后由守护进程负责管理网络隧道与数据传输路径。

图源:DoubleZero Whitepaper

图源:DoubleZero Whitepaper

在具体执行过程中,调度系统会根据实时网络状态分配最优路径,并优先选择性能更高、延迟更低的链路。同时,通过对节点贡献度的评估(例如基于边际贡献的模型),实现更加公平与高效的资源分配。

这种机制使网络能够在复杂环境中自动优化路径,从而持续提升整体性能。

DoubleZero 的任务执行流程

DoubleZero 的运行流程可以分为多个阶段。首先,用户或系统提交数据传输或通信任务。随后,数据进入网络入口层,由 FPGA 硬件进行过滤与签名验证,确保数据合法性。

接下来,经过验证的数据会被传输至内环专用光纤网络,通过最优路径快速到达目标节点。在共识节点完成处理后,相关性能数据会被反馈至链上系统,用于后续结算与优化。

整个流程形成一个闭环,使任务能够高效完成并持续优化网络运行状态。

DoubleZero 的计算验证机制

DoubleZero 的验证机制结合硬件与链上逻辑,实现多层安全保障。在入口层,FPGA 硬件负责过滤重复数据、检测攻击流量并验证签名,从而在源头保证数据质量。

在链上层面,智能合约会持续监控节点的性能指标,例如延迟与吞吐量。如果某条链路无法满足要求,系统会自动降低其权重或将其隔离,从而确保整体网络的稳定性与可靠性。

这种“硬件 + 合约”的验证模式,使 DoubleZero 在安全性与效率之间取得平衡。

DoubleZero 的激励与惩罚机制

为了维持网络高效运行,DoubleZero 引入了基于性能的激励机制。贡献者的奖励与其提供的网络质量直接相关,例如低延迟、高稳定性的链路将获得更高收益。

在经济层面,用户支付的服务费用会转化为代币需求,而部分机制可能通过销毁或锁定代币来增强其价值。与此同时,节点需要进行质押,以保证其提供服务的可靠性。

对于表现不佳或存在异常行为的节点,系统会通过降低收益、扣减质押或移除其参与资格等方式进行惩罚,从而维持网络整体质量。

DoubleZero 的核心机制如何协同工作

DoubleZero 的高性能来源于多层机制的协同作用。双环架构将过滤与传输分离,使网络既安全又高效;任务调度机制动态优化路径,提升资源利用率;验证机制确保数据与行为的可信性;激励机制则驱动参与者持续优化性能。

这些机制共同形成一个闭环:资源贡献、任务调度、执行传输、结果验证以及奖励分配相互连接,从而不断提升网络效率。据相关数据,该系统可将区块链通信与共识效率提升约 77%。

总结

DoubleZero 通过硬件、软件与链上机制的深度结合,构建了一个高效且可信的去中心化通信网络。其核心在于通过任务调度与验证机制优化数据传输路径,从而突破公共互联网的性能限制。

随着 Web3 应用对低延迟与高吞吐的需求不断增长,DoubleZero 有望成为关键的基础设施之一,为区块链网络提供更强的性能支撑。

FAQs

DoubleZero 如何运作?

通过任务调度、数据过滤、光纤传输、结果验证与奖励结算构成完整流程。

DoubleZero 的核心技术是什么?

双环架构、FPGA 硬件过滤与链上验证机制。

为什么需要去中心化调度?

可以避免单点故障并提升资源分配效率。

DoubleZero 如何保证数据安全?

通过硬件过滤与链上合约验证双重机制实现。

DoubleZero 的性能优势在哪里?

主要体现在低延迟(<10ms)与通信效率提升。

相关文章

CKB:闪电网络促新局,落地场景需发力

什么是 ZEROBASE?

什么是加密货币中的完全稀释估值(FDV)?

牛市逃顶指标 25 项全分析

什么是 Fartcoin (FARTCOIN)?Solana 爆火 AI Meme 币指南